## AD9833 DDS レジスタを PIC で書くメモ (改訂版)

2019/01/05 JA5FP

AD9833 DDS は、 $0\sim20 \mathrm{MHz}$  の出力レンジ・28 ビット分解能・サイン波/三角波/方形波の出力・周波数/位相変調が可能な信号源です。制御は 3 線式 SPI ですので、その機能を有する PIC 16F1823 マイクロプロセッサ等で簡単に行うことができます。それ等のデバイスの詳細は、次の URL からダウンロードできます。

www. anal og. com/medi a/j p/techni cal -documentati on/data-sheets/AD9833\_JP. pdf http://ww1.microchip.com/downloads/jp/DeviceDoc/41413C\_JP.pdf

ただし、AD9833 のレジスタは"16 ビット・ワード" として説明されていますが、PIC は"8 ビット・バイト" を取り扱いますので、インターフェースの設定に悩まされます。そこで、その疑問解明を目的にして実回路で確認しましたので、本稿ではその結果をメモとして残します。

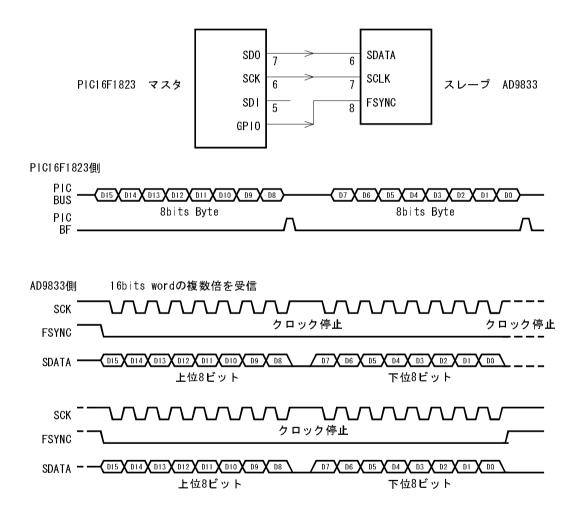

図1に、インターフェースと書き込みタイミングを示します。

図 1: PIC SPI による AD9833 のレジスタ書き込み

もちろん、PIC 側は SPI マスタとして動作します。データが SSP1BUF にロードされると、SCK からクロックと SDO からデータの送出が行われ、8 ビット送り終えると BF が立ち上がります。これで PIC 内部では 1 バイトの送信が完了しますので、SCK をアイドリング状態に保ちます。ソフトウェアが次のデータである 8 ビット・バイトを SSP1BUF にロードして、SCK と SDO が出力されることになります。

いっぽう、AD9833 側では SCLK に同期してデータ  $D_{15}$  から  $D_0$  までをレジスタに収納します。ここで、FSYNC がローレベルの間をデータ長として、16 ビット・ワードの整数倍まで認識します。ですから、制御レジスタ、周波数/位相レジスタへの書き込みを 1 つの FSYNC 周期内で行うことができます。

次のプログラム例は、単純に  $2.4576 \mathrm{MHz}$  基準周波数から  $137.5 \mathrm{kHz}$  の方形波クロックを出力する サンプルです。この場合の VOUT 出力は  $\mathrm{MSB}/2$  を使用しますので、 $\mathrm{MSB}$  としては  $137.5 \mathrm{kHz} \times 2 = 275 \mathrm{kHz}$  を生成することになります。 算式は次のとおり。

$$FREQ0 = 275 \ 10^3 \times 2^{28} / 2.4576 \ 10^6 = 30,037,333$$

この値は 16 進法では 0x1ca5555 となります。AD9833 の周波数レジスタは 28 ビット構成ですので、ここで 14 ビットの MSB と 14 ビットの LSB に分解します。すなわち、MSB が 0x0729 と LSB が 0x1555 です。それぞれの前に周波数レジスタへのアドレス (0b01) を付加して、LSB は 0x5555 と MSB は 0x4729 として SDATA を送ります。

可変周波数・周波数変調/位相変調・出力波形等の応用は各パラメータを変更すれば可能ですが、この段階では省略します。

```

//"gy9833.c" ver.0r00 (c) 2019.01.05 JA5FP

//This program may be compiled with MPLAB XC8 C Compiler on MPLAB X IDE v2.20.

//Target hardware is PIC16F1823 and DDS unit GY9833 replaced XTAL 2.4576MHz.

//The functions are:

// (1) to learn how to configure 16F1823`s SPI

(2) to set simply specific frequency to AD9833 DDS

#include <xc. h>

#include <pi c16f1823. h>

#pragma config FCMEN=OFF, IESO=OFF, CLKOUTEN=OFF, BOREN=ON, CPD=OFF, CP=OFF

#pragma config MCLRE=OFF, PWRTE=OFF, WDTE=OFF, FOSC=ECM

#pragma config LVP=OFF, BORV=LO, STVREN=OFF, PLLEN=OFF, WRT=OFF

voi d devi ce1823(voi d) {

// hardware setting

APFCON=0b10000100;

// RX=RA1

ANSELA=0b00000000:

// digital portA

ANSELC=0b00000000;

// digital portC

// RA5=CLK, RA4=/PTT, RA3=D1, RA2=1PPS,

TRI SA=0b00101111;

// RA1=NMEA, RAO=DO

// RC5=D3, RC4=D2, RC3=FSYNC, RC2=SDATA,

// RC1=DDI, RC0=SCLK

// WPU enable

// WPU portA

// WPU portC

// SPI master mode, clock=Fin/4=614.4kHz

TRI SC=0b00110010:

OPTI ON_REG=0b00000010;

WPUA=0b00001001;

WPUC=0b00110010;

SSP1C0N1=0b00110000;

SSP1C0N3=0b00000000;

SSP1STAT=0b00000000;

I NTCON=0b00100000;

}// devi ce1823()

void spi (unsigned int variable){

SSP1BUF=variable; while(!BF); // transmitt 8bits Byte via SPI

}// spi ()

void main(void){

devi ce1823();

// initialize 16F1823

RC3=1; RC3=1; // SPI idle state

RC3=0; RC3=0; // SPI start

// reset AD9833 register

spi (0x21);

spi (0x40);

// output from MSB/2

spi (0x55);

// frequency register with 14LSB

spi (0x55);

// remained 8bits

// frequency register with 14MSB

spi (0x47);

spi (0x29);

// remained 8bits

spi (0x20);

// unreset AD9833 register

// output from MSB/2

spi (0x40);

RC3=1; RC3=1;

// continue DDS

while(1){;}

}// main()

```